## IP cores & SDK

partner <sub>Titanium</sub>

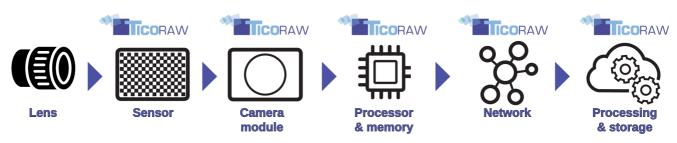

## Unleash image sensor dataflows

Engineered at intoPIX, TicoRAW is an innovative, lossless quality, low-power, low-memory and line-based image processing and compression technology created to unleash image sensor dataflows.

Thanks to its innovative processing and coding, the full power of the image sensor is preserved while reducing the bandwidth and storage needs. It offers high image quality and the capability to manage high resolution, high frame rate and high dynamic range workflows. TicoRAW is the world's first codec that can offer compression efficiency with such low complexity.

TicoRAW is a perfect solution for XR, medical, automotive (ADAS), human and machine vision, professional and consumer cameras (stills and videos), drones or mobiles devices. The technology is extremely low-power and tiny in ASIC or FPGA, fast and powerful in CPU or GPU, and suitable for latency-critical environments.

#### **Technology benefits**

- > High quality RAW

- Supports image sensors up to 16bit; with High Dynamic Range (HDR)

- Compresses down to 1bit per pixel (2:1 to 16:1)

- Perfect for human and machine vision

- > From 1 megapixel to 200 megapixels

- Includes embedded proxy decoding mode

- > FPGA & ASIC IP-cores

- Extremely low resource usage, low-memory, low-power

- Microsecond line-based latency

- > Developer SDK for CPU & GPU

- Powerful, real-time or faster than real-time

## Vhere can TicoRAW be implemented?

- Reduce your power consumption. Process and manage more pixels from the sensor.

- · Reduce your bandwidth during real-time transmission over network infrastructures without affecting the latency.

- Support higher resolution, high frame rate and high dynamic range easily.

- Reduce your memory bandwidth in the image processing pipeline (ISP).

- · Efficiently decrease the stored RAW image data on the storage media. (RAW 10x smaller)

- · Increase your decoding speed while retaining the sensor data needed for a complete control of the RAW processing pipeline.

# **Specifications and implementations**

|             |                          | TicoRAW ENCODER & DECODER                                                                                    |  |  |

|-------------|--------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| IMAGE/VIDEO | Color Filter Array (CFA) | RAW Bayer & Bayer (RGGB,), and other RAW CFA such as RCCB, RYYCy, (Optional grayscale and 4:2:2 modes)       |  |  |

|             | Bit depth                | 8 / 10 / 12 / 14 / 16 bits per component                                                                     |  |  |

|             | Resolution               | Any up to 20.480 x 10.240 pixels                                                                             |  |  |

|             | Frame rates              | Any (depending on ASIC / FPGA IP-core or Developer SDK configuration)                                        |  |  |

| PROCESSING  | Quality                  | Mathematically lossless / Near-lossless / Visually lossless / Lossy down to 1bpp                             |  |  |

|             | Rate control             | CBR (constant bit rate) operation (optional Constant Quality mode) Adjustable down to 1bpp ( $^{\sim}$ 10:1) |  |  |

|             | Latency                  | (Sub) Intra-frame: down to 0.1 millisecond                                                                   |  |  |

|             | Proxy mode               | Downscaler in TicoRAW decoder for fast analysis, proxy viewing & editing                                     |  |  |

|                |                                     | TicoRAW IP cores                                                                        | FastTicoRAW SDK                                                                    |

|----------------|-------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| IMPLEMENTATION | Platform                            | Intel FPGA<br>Cyclone V, Arria V, Stratix V, Cyclone 10,<br>Arria 10, Stratix 10        | GPU: x86-64 Intel<br>CPU<br>OS: Windows, Linux, macOS                              |

|                | Low complexity<br>& fast processing | Small footprint, ultra low memory<br>& low-power (no ext DDR)<br>Various configurations | Highly parallelized GPU SDK processing<br>Compatible CPU SDK<br>(SSE 4.1 or newer) |

|                | Real-time operation                 | Line-based latency (< 1 millisecond)                                                    | < 1 frame                                                                          |

### IP core releases

|                                           |                  |                      |                                           | Max frames per sec. |                |                |

|-------------------------------------------|------------------|----------------------|-------------------------------------------|---------------------|----------------|----------------|

| IP-CORES                                  | Color            | Sensor               | Resolution examples                       | at 100              | at 250         | at 300         |

| -ENC / -DEC                               | sampling         | bit depth            |                                           | MHz*                | MHz*           | MHz*           |

| IPX-TICO-RAW-2K                           | RAW CFA          | 8, 10, 12,           | 2048 X 1080                               | 335                 | 839            | 1006           |

| (Up to 2048-pixels width)                 | Bayer            | 14, 16               | 2048 X 2048                               | 177                 | 442            | 530            |

| IPX-TICO-RAW-4K                           | RAW CFA          | 8, 10, 12,           | 4096 X 2160                               | 84                  | 209            | 250            |

| (Up to 4096-pixels width)                 | Bayer            | 14, 16               | 4096 X 4096                               | 44                  | 110            | 132            |

| IPX-TICO-RAW-8K (Up to 8192-pixels width) | RAW CFA<br>Bayer | 8, 10, 12,<br>14, 16 | 7680 X 4000<br>8192 X 4320<br>8192 X 8192 | 60<br>21<br>11      | 60<br>52<br>28 | 72<br>62<br>33 |

### CONTACT INTOPIX FOR YOUR OWN CUSTOM IP CORE & SDK CONFIGURATION

#### **HEADQUARTERS:** intoPIX SA

Rue Emile Francqui 9 B-1435 Mont-Saint-Guibert - Belgium Tel.: +32 10 23 84 70 sales@intopix.com **EUROPE/MIDDLE EAST:** sales.emea@intopix.com

CHINA: sales.china@intopix.com

JAPAN: sales.japan@intopix.com

S. KOREA: sales.korea@intopix.com

USA/CANADA: sales.na@intopix.com

<sup>\*</sup> Max Frequency (MHz) of the IP-cores can be adjusted according to your selected pixel per clock architecture and your targeted FPGA